这几天做的一个模块设计需要实现一个50%占空比的奇数分频的电路,和小D一起研究了一下,总结了几个方法

关于奇数分频关键在于如何用分频器打出半个时钟周期。下面以3分频为例来说明。

1,将原时钟2倍频,再偶数6分频。这个方法不常用,因为倍频的电路可能需要更多的资源来实现,一般没有这么做的必要。

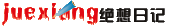

2,用两个计数器同时计数,计数周期为3,在第一个计数周期输出高,其余两个周期输出低。唯一不同的是,这两个计数器,一个用原时钟的上升沿去打,一个用下降沿去打。其实这样打出来的波形的脉宽因为上下沿的关系刚好错开了半个时钟周期,所以最后再把两个信号用或门打出来就可以了,图形如下,A,B分别为上沿和下沿打出来的信号

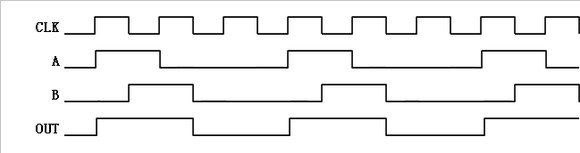

3,先实现小数分频,也就是1.5分频,再2分频得到3分频信号。这个关键在于实现小数分频,其实跟上面原理略同,也是要打出那半个时钟周期。其实现方法是在最后的一个计数周期将原时钟反向,于是下一个下降沿变成上升沿,从而得到半个时钟周期。具体设计,首先一个循环计数器,两个计数周期(设为0和1),计数为0的周期,输出信号为低,计数为1的周期时,输出为高,并且此时将输入原时钟反向。然后将此计数器的输出信号(也就是得到的1.5分频信号)再用寄存器打一拍,就是2分频,便得到3分频信号。结构如下,时序图懒得画了……

其实方法3用到的寄存器资源要比方法2少,因为只需要一个计数器,但是对于方法3中的计数器,其输入时钟相当于由原时钟产生的一个异步信号,而且最后那个寄存器的输入时钟也是由原时钟产生的一个分频时钟,个人认为方法3比较方法2,应该是不适合同步设计的。

对于任意计数分频,方法同上,只需改变相应计数周期即可得到。

关于50%占空比奇数分频的实现

心情分类

推荐日记

分享排行